嵌入式FPGA技術即將在數(shù)據(jù)中心業(yè)界普及推廣

現(xiàn)如今的數(shù)據(jù)中心管理人員們希望他們的設施具有更高的可重構性和可編程性,而不再如同舊PC時代必須更換硬件才能跟上不斷變化的標準和協(xié)議。到目前為止,可重構性尚不存在,協(xié)議的改變則很容易要求數(shù)據(jù)中心運營商們必須更換設施中的每個芯片。而伴隨著嵌入式FPGA(eFPGA)技術的出現(xiàn),這些問題正在逐步消失。這種技術不僅可以在芯片安裝到數(shù)據(jù)中心后,實現(xiàn)重新配置,還可以將處理器性能提高40-100倍。諸如美國國防高級研究計劃局(Defense Advanced Research Projects Agency,簡稱DARPA)、SiFive公司、哈佛大學、美國桑迪亞國家實驗室和Hiper Consortium公司等相關業(yè)界領軍都在設計eFPGAs。

但令人驚訝的是,大多數(shù)業(yè)內(nèi)人士把并不明白eFPGA是什么,也不清楚其與諸如Xilinx,Altera等獨立模型的傳統(tǒng)的FPGA有什么不同之處。事實上,這兩種技術是不同的,甚至并不存在相互競爭的關系。

FPGA與eFPGAs

eFPGA是一種知識產(chǎn)權(IP)模塊,可將完整的FPGA集成到SoC或任何類型的集成電路中。這是相對較新的,但將芯片轉換為IP模塊的想法早已存在。正如RAM、serdes、PLL和處理器從獨立芯片轉向常規(guī)IP模塊一樣,F(xiàn)PGA也是一個IP模塊。

FPGA在可編程互連結構中結合了一系列可編程/可重新配置的邏輯塊。FPGA芯片的外部邊緣由GPIO、serdes和專用PHY(包括DDR3 / 4)組成。在高級FPGA中,I / O環(huán)大約是芯片的四分之一,“結構”大約是四分之三。這種結構主要是當今FPGA芯片中的互連;其面積的20-25%是可編程邏輯,75-80%是可編程互連。

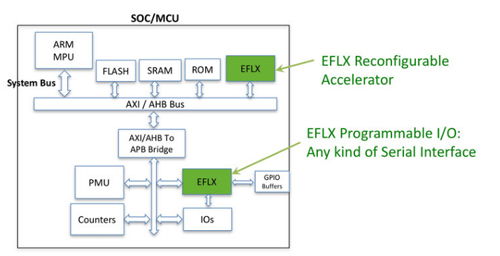

eFPGA是一種沒有GPIO、serdes和PHY的FPGA架構。相反,它使用標準的數(shù)字信號連接到芯片的其余部分,從而實現(xiàn)寬的快速芯片互連。

eFPGA如何扮演加速器的作用

每個芯片都有一個或多個Arm、ARC、Mips或其他處理器執(zhí)行代碼。對于占用大部分處理器帶寬的任務而言,硬件中的加速器通常可以在更短的時間內(nèi)處理任務。(當然,加速器不會取代處理器,它只是加速了大部分工作量密集型任務。)但是,如果使用硬連線加速器,則只能加速一項任務。

通過eFPGA對加速器進行重新配置,可以根據(jù)工作負載需求或不同的客戶/應用程序的需求加速執(zhí)行多項任務。這種將關鍵代碼加速一個或兩個數(shù)量級的能力是每個芯片設計人員都應該評估的。將處理器性能提高40-100倍便是其主要的競爭優(yōu)勢。

現(xiàn)在,eFPGAs可以以任何最流行的流程節(jié)點和任何規(guī)模尺寸,以及可選的MAC / RAM獲得,以提供從MCU到數(shù)據(jù)中心的可重新配置加速。

有關使用eFPGA作為加速器的更多詳細信息,請點擊此應用筆記鏈接。其描述了將eFPGAs連接到通用總線的確切實現(xiàn)方式,并提供了多個詳細的性能比較,以便您可以開始評估eFPGAs。

成本優(yōu)勢

設計ASSP、ASIC和SoC的成本和時間不斷增加。這種情況是一個挑戰(zhàn),因為這意味著芯片市場必須更大,才能提供良好的投資回報——而且設計時間長,使得難以滿足不斷變化的客戶規(guī)格和標準。

在數(shù)據(jù)中心中,客戶多年來一直在尋求可重構性。當標準不斷發(fā)展時,數(shù)據(jù)中心不再需要升級叉車,而需要的是可編程芯片,以便在不觸及硬件的情況下升級其功能。它還使數(shù)據(jù)中心運營商可以選擇定制化,以獲得更大的競爭優(yōu)勢。正如微軟的Doug Burger在2016年度現(xiàn)場可編程邏輯與應用國際會議(FPL)上所說的那樣,可重新配置的云服務將改變世界,使其能夠重新編程數(shù)據(jù)中心的硬件協(xié)議:網(wǎng)絡、存儲和安全。而將FPGA技術添加到混合中是實現(xiàn)這一目標的關鍵。

另一個可以節(jié)省大量成本的例子是微控制器。在較老的工藝節(jié)點(如90納米)中,掩膜成本便宜,線卡可能有幾十或幾百個版本。例如,這種類型為每個客戶提供了小的差異,例如,串行接口(SPI、I2C、UART等)的數(shù)量和類型。但是現(xiàn)在先進的微控制器正在向40納米技術轉移,其中每個掩膜的成本為100萬美元,微控制器制造商需要一種可編程的方式來定制他們的芯片,并提供多個SKU。增加的這個功能也為他們的客戶打開了自己定制MCU的途徑,類似于他們現(xiàn)在如何為機上處理器編寫C代碼。當今的一些微控制器,例如賽普拉斯的PSoC,提供了一些有限的可定制性。但是,只有eFPGA才能提供更多可擴展的可定制性。

多個市場適合多款應用程序

eFPGA陣列可以為芯片設計人員在任何需要靈活性的地方提供服務,以解決不確定性或不斷變化的標準,或以高性能滿足一系列市場需求。從大型網(wǎng)絡芯片到小型MCU /物聯(lián)網(wǎng)芯片,廣泛的應用非常適合eFPGAs。在40納米以及MCU / IoT等應用中,重點在于功耗;因此,設計eFPGA的企業(yè)組織機構優(yōu)化其產(chǎn)品以具有更多電源管理模式,低電壓狀態(tài)保持和其他功能。在28 / 16納米應用程序中,重點在于性能,所以ePGAs可以針對該要求進行優(yōu)化。當eFPGA在控制路徑或數(shù)據(jù)路徑中工作時,其性能最高,并且必須遵循周圍硬連線RTL ASIC的頻率。在這種情況下,客戶通常在1000個或更少的LUT中使用eFPGA,在觸發(fā)器之間植入一個或兩個LUT階段的快速控制邏輯。 I / O需求往往很大,特別是在投入方面。性能要求相對較低的是I / O控制,例如MCU或IoT設備,其中eFPGA可以啟用本地I / O處理,以根據(jù)I / O功能需要,通過不激活MPU或在其中實現(xiàn)額外的串行接口來降低整體系統(tǒng)功率。

以下只是eFPGAs在今天所服務的幾個市場:

網(wǎng)絡:可編程解析器、網(wǎng)絡協(xié)議、安全協(xié)議和存儲協(xié)議;

數(shù)據(jù)中心加速

無線基站DFE(數(shù)字化前端);

MCU:可重新配置的I / O、用于卸載MPU的I / O處理、可重新配置的加速器;

SoC:I/O mux、可重構I / O、可重構加速器;

固態(tài)硬盤:可編程時序和ECC;

航空航天/國防:集成整合的FPGA體積更小,重量更輕,功耗更低,并且可以在輻射強化工藝和/或可信晶圓廠

未來的數(shù)據(jù)中心

eFPGAs正在改變芯片的設計流程,從而改變數(shù)據(jù)中心的構建和維護方式。隨著時間的推移,嵌入式FPGA技術預計會變得更加普遍,以至于它們將可以從180nm到7nm的每個主要晶圓廠獲得,從而支持廣泛的應用。

有了數(shù)據(jù)中心的可重構性,運營商將擁有比以往更大的靈活性。為了響應不斷變化的協(xié)議或標準,芯片可以在系統(tǒng)中進行更新,運營商也將能夠采用eFPGAs來加速某些任務或工作負載所需的處理器性能。其結果將有助于成本的節(jié)省,以及減少維護和開發(fā)的費用,這是每家數(shù)據(jù)中心經(jīng)理都在追求的目標。

責任編輯:任我行

- 相關閱讀

- 碳交易

- 節(jié)能環(huán)保

- 電力法律

- 電力金融

- 綠色電力證書

-

碳中和戰(zhàn)略|趙英民副部長致辭全文

2020-10-19碳中和,碳排放,趙英民 -

兩部門:推廣不停電作業(yè)技術 減少停電時間和停電次數(shù)

2020-09-28獲得電力,供電可靠性,供電企業(yè) -

國家發(fā)改委、國家能源局:推廣不停電作業(yè)技術 減少停電時間和停電次數(shù)

2020-09-28獲得電力,供電可靠性,供電企業(yè)

-

碳中和戰(zhàn)略|趙英民副部長致辭全文

2020-10-19碳中和,碳排放,趙英民 -

深度報告 | 基于分類監(jiān)管與當量協(xié)同的碳市場框架設計方案

2020-07-21碳市場,碳排放,碳交易 -

碳市場讓重慶能源轉型與經(jīng)濟發(fā)展并進

2020-07-21碳市場,碳排放,重慶

-

兩部門:推廣不停電作業(yè)技術 減少停電時間和停電次數(shù)

2020-09-28獲得電力,供電可靠性,供電企業(yè) -

國家發(fā)改委、國家能源局:推廣不停電作業(yè)技術 減少停電時間和停電次數(shù)

2020-09-28獲得電力,供電可靠性,供電企業(yè) -

2020年二季度福建省統(tǒng)調(diào)燃煤電廠節(jié)能減排信息披露

2020-07-21火電環(huán)保,燃煤電廠,超低排放

-

四川“專線供電”身陷違法困境

2019-12-16專線供電 -

我國能源替代規(guī)范法律問題研究(上)

2019-10-31能源替代規(guī)范法律 -

區(qū)域鏈結構對于數(shù)據(jù)中心有什么影響?這個影響是好是壞呢!