智能變電站動態(tài)重構(gòu)技術(shù)研究

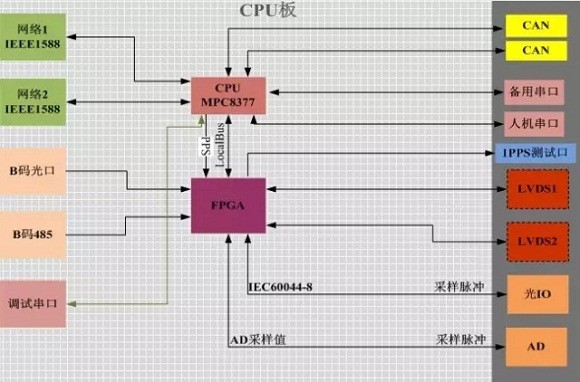

2.2.1CPU板

CPU板包括CPU主板和CPU的FPGA板

1)CPU板主板

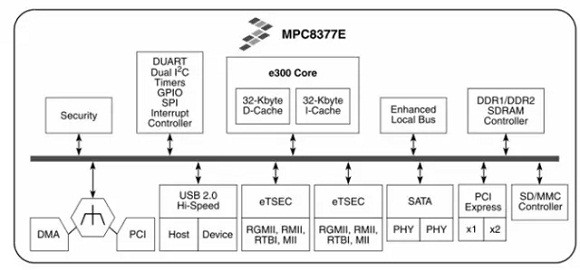

CPU插件的主CPU采用MPC8377E。MPC8377E處理器采用e300core,主頻可達(dá)667MHz;帶MMU,DDR2內(nèi)存最高400MHz;32位LocalBus,最高133MHz,支持NandFlash啟動;32位PCI總線,最高66MHz;2個PCI-E接口;2個SATA接口;2個10/100/1000Mbit的以太網(wǎng)接口;1個USB2.0接口;2個UART;2個I2C;1個SPI。如圖4所示。

圖4CPU板插件硬件框架

CPU板主變的主要資源如圖5所示。

圖5MPC8377模塊框圖

2)CPU板的FPGA板

CPU板的FPGA實現(xiàn)的功能比較復(fù)雜,為數(shù)據(jù)處理的核心部分。

FPGA同時接收左向和右向網(wǎng)絡(luò)板FPGA的數(shù)據(jù),并按照相應(yīng)的順序填寫到SDRAM中,并使能中斷信號,提示CPU可以接收網(wǎng)絡(luò)數(shù)據(jù)。

由于SDRAM不能同時讀寫。當(dāng)CPU響應(yīng)FPGA中斷接收數(shù)據(jù)時,將會同時占用FPGA和一片SDRAM的LocalBus,如果此時網(wǎng)絡(luò)板FPGA有數(shù)據(jù)包傳遞進(jìn)來的話,就只能緩沖到第二塊SDRAM。然后發(fā)起中斷,提示數(shù)據(jù)到來,CPU將會讀取第二塊SDRAM,以此類推,由兩塊SDRAM實現(xiàn)了雙口RAM的功能。

由于CPU與FPGA之間只有一個LocalBus接口,當(dāng)CPU與SDRAM進(jìn)行數(shù)據(jù)通信時,LocalBus會被占用,此時CPU無法訪問FPGA,最好增加一個SPI接口,CPU可以通過SPI接口適時訪問FPGA。

2.2.2網(wǎng)絡(luò)接口板

每個網(wǎng)絡(luò)接口板配置8個網(wǎng)絡(luò)接口。每個以太網(wǎng)口均有l(wèi)ink及act指示燈,用于表征各網(wǎng)絡(luò)接口及接口板的工作狀態(tài)。通過更換元器件可實現(xiàn)網(wǎng)絡(luò)的電接口或光接口。網(wǎng)絡(luò)接口板通過FPGA實現(xiàn)以太網(wǎng)口驅(qū)動、網(wǎng)絡(luò)接口板與CPU板的通信。網(wǎng)絡(luò)接口板與背板聯(lián)絡(luò),為光纖接口和CPU通信傳遞信息。網(wǎng)絡(luò)接口板與CPU板之間采用光纖通信。

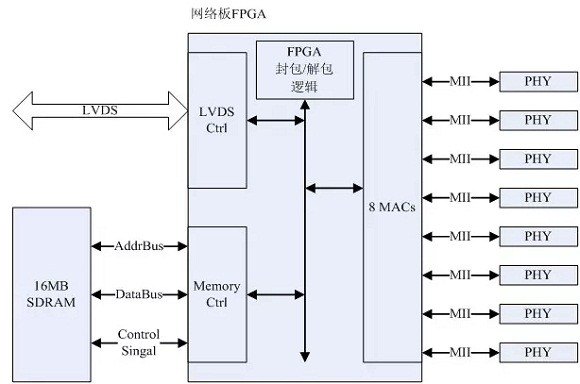

網(wǎng)絡(luò)接口網(wǎng)絡(luò)板硬件框圖如圖6所示,主要由以下三部分組成:(1)FPGA模塊,主要實現(xiàn)FPGA封包解包邏輯、8個10/100MMACs、LVDS高速總線控制器以及SDRAM存儲器控制器。(2)SDRAM模塊,主要實現(xiàn)網(wǎng)絡(luò)數(shù)據(jù)幀的存儲、轉(zhuǎn)發(fā)。(3)PHYs模塊,包括8個10/100M以太網(wǎng)PHY芯片。PHY芯片建議選RTL8208B,該芯片為8路10/100Base-T/TX和100Base-FXPHY,也可以選擇RTC8201或IP101A等芯片。板采用子母板設(shè)計方式。

圖6網(wǎng)絡(luò)板FPGA功能模塊

2.3FPGA功能設(shè)計

2.3.1系統(tǒng)邏輯

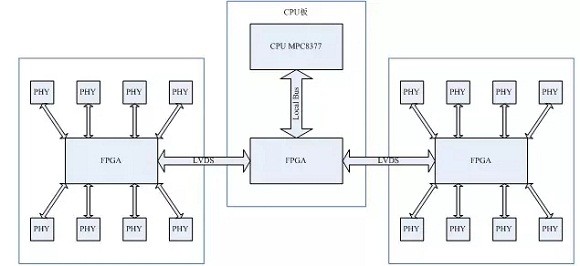

FPGA設(shè)計包括CPU板FPGA設(shè)計和網(wǎng)絡(luò)板FPGA設(shè)計兩部分。網(wǎng)絡(luò)板的FPGA主要實現(xiàn)擴展網(wǎng)絡(luò)功能和網(wǎng)絡(luò)數(shù)據(jù)的解碼功能;CPU板的FPGA主要實現(xiàn)CPU與FPGA之間的數(shù)據(jù)通信以及與網(wǎng)絡(luò)板FPGA的交互數(shù)據(jù)的功能。功能如圖7所示。

圖7FPGA系統(tǒng)連接圖

2.3.2FPGA邏輯功能

其主要功能是完成8個以太網(wǎng)MAC與串行的高速LVDS總線之間的通信。可以實現(xiàn)8個10/100MMAC與8個PHY芯片進(jìn)行數(shù)據(jù)交互。為每一個MAC設(shè)計兩個幀的緩沖區(qū),每個緩沖區(qū)大小為2048字節(jié);同時可以實現(xiàn)LVDS本方案考慮使用LVDS接口實現(xiàn)FPGA之間的互聯(lián)。FPGA收到網(wǎng)絡(luò)數(shù)據(jù)包之后,通過8b/10b編碼轉(zhuǎn)換成(至少)1Gbps的網(wǎng)絡(luò)數(shù)據(jù)流,將其傳輸?shù)紺PU板的FPGA。

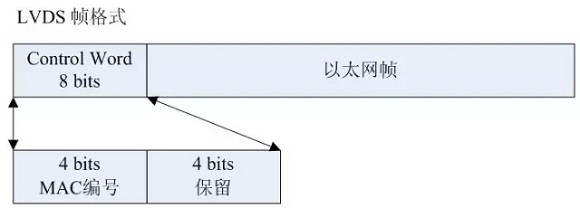

但由于封包解包邏輯8個以太網(wǎng)MAC的數(shù)據(jù)是并行的,而LVDS總線是串行的,所以還要考慮:LVDS選擇性的從8個MAC讀取數(shù)據(jù)傳輸。其選擇MAC的順序是1至8,而后繞回到1;其選擇依據(jù)是當(dāng)前MAC的緩沖區(qū)是否有合法的數(shù)據(jù)幀,如果有則發(fā)送,沒有則直接跳過。LVDS傳輸?shù)膸袷饺鐖D8所示。

圖8LVDS幀格式

結(jié)論

本文根據(jù)智能變電站二次功能實現(xiàn)的工程設(shè)計,研究了智能變電站二次系統(tǒng)動態(tài)重構(gòu),提出了動態(tài)重構(gòu)功能的硬件及軟件解決方案。在研究過程中,以智能變電站二次功能實現(xiàn)的各個環(huán)節(jié)為基礎(chǔ),研究了智能變電站基于信息共享的二次設(shè)備功能軟件構(gòu)造技術(shù)及功能軟件組件實現(xiàn)技術(shù)。

重構(gòu)技術(shù)在智能變電站運行及維護(hù)工作中的自愈、自適應(yīng)、自恢復(fù)等方面具有一定優(yōu)勢,為智能變電站二次系統(tǒng)提供了新的手段,增加了二次系統(tǒng)運行的靈活性,有利于推動變電站智能化進(jìn)程。

責(zé)任編輯:電朵云

- 相關(guān)閱讀

- 能源互聯(lián)網(wǎng)

- 電動汽車

- 儲能技術(shù)

- 智能電網(wǎng)

- 電力通信

- 電力軟件

- 高壓技術(shù)

-

中日韓動力電池企業(yè)涌入 不想燒錢的歐洲人怎么辦

-

比亞迪現(xiàn)在分拆電池業(yè)務(wù)是不是晚了?

-

飛輪儲能制動能量回收裝置在地鐵行業(yè)的應(yīng)用

2018-06-07飛輪儲能

-

RS-SUNNET光纖網(wǎng)卡,5G時代的光纖接入首選網(wǎng)絡(luò)設(shè)備

-

電線變“光纖”,千兆組網(wǎng),百兆光纖無損覆蓋,華為路由Q2厲害了

-

制作10kV電纜終端頭的關(guān)鍵,你知道嗎?